Микропроцессорная система какого типа разрабатывается чаще всего?

- разработка не требуется, используются готовые системы

- компьютер

- микрокомпьютер

- (Правильный ответ) микроконтроллер

Микропроцессорная система какого типа не обеспечивает управление внешними устройствами?

- компьютер

- контроллер

- (Правильный ответ) все типы обеспечивают управление внешними устройствами

- микроконтроллер

Какая структура шин адреса и данных обеспечивает большее быстродействие?

- (Правильный ответ) немультиплексированная

- быстродействие от структуры не зависит

- двунаправленная

- мультиплексированная

Какой тип обмена обеспечивает гарантированную передачу информации любому исполнителю?

- синхронный и асинхронный

- ни синхронный, ни асинхронный

- (Правильный ответ) асинхронный

- синхронный

Что такое операнд?

- (Правильный ответ) код данных

- адрес данных

- адрес адреса данных

- адрес команды

- код команды

Какой метод адресации предполагает размещение операнда внутри выполняемой программы?

- абсолютная адресация

- операнд всегда находится внутри программы

- косвенная адресация

- (Правильный ответ) непосредственная адресация

- регистровая адресация

К какой группе относятся команды сдвига кодов?

- (Правильный ответ) логические команды

- команды управления процессором

- арифметические команды

- команды пересылки

- команды переходов

Какие команды не формируют выходной операнд?

- арифметические команды

- логические команды

- команды сдвигов

- команды пересылки

- (Правильный ответ) команды переходов

Чем ограничена глубина вложений циклов вызова подпрограмм в микроконтроллере?

- разрядностью счетчика команд

- (Правильный ответ) глубиной стека

- объемом памяти программ

- объемом памяти данных

Сколько раз можно изменить содержимое памяти программ на основе ПЗУ масочного типа?

- около 1000 раз

- (Правильный ответ) один раз на стадии изготовления МК

- одни раз на стадии программирования пользователем

- неограниченное число раз

Какой параметр выходного сигнала изменяется при широтно-импульсной модуляции?

- (Правильный ответ) скважность

- уровень логической «1»

- уровень логического «0»

- частота

Какой тип логической функции позволяет реализовать объединение «квазидвунаправленных» выходов микроконтроллера?

- константа «1«

- «ИЛИ«

- сложение по модулю 2

- (Правильный ответ) «И«

Как зависит ток потребления микроконтроллера от напряжения питания?

- квадратично

- не зависит

- (Правильный ответ) приблизительно линейно

- обратно пропорционально

Где хранятся биты признаков результата операций микроконтроллеров подгруппы PIC16F8Х?

- в регистре таймера/счетчика

- в регистре OPTION

- в регистре INTCON

- (Правильный ответ) в регистре STATUS

Какова разрядность таймера/счетчика TMR0 микроконтроллеров подгруппы PIC16F8Х?

- (Правильный ответ) 8

- 14

- 16

- 4

Что дает двухступенчатый конвейер исполнения команд в PIC-микроконтроллерах?

- возможность удвоения тактовой частоты

- возможность динамического предсказания переходов

- возможность параллельного исполнения двух команд

- (Правильный ответ) возможность одновременной выборки и исполнения команд

Где хранится указатель адреса при косвенной адресации данных в микроконтроллерах подгруппы PIC16F8Х?

- в регистре STATUS

- в регистре PCLATH

- (Правильный ответ) в регистре FSR

- недоступен пользователю

Какой бит определяет режим работы таймера/счетчика микроконтроллеров подгруппы PIC16F8Х?

- бит TO регистра STATUS

- бит T0IE регистра INTCON

- бит PSA регистра OPTION

- (Правильный ответ) бит T0CS регистра OPTION

Какой бит определяет режим использования предделителя микроконтроллеров подгруппы PIC16F8Х?

- (Правильный ответ) бит PSA регистра OPTION

- бит TO регистра STATUS

- бит T0CS регистра OPTION

- бит T0IE регистра INTCON

Где хранится информация о содержимом пределителя микроконтроллеров подгруппы PIC16F8Х?

- в регистре OPTION

- (Правильный ответ) недоступна

- в регистре TMR0

- в регистре FSR

Где хранятся биты конфигурации микроконтроллеров подгруппы PIC16F8Х?

- в регистре EEDATA

- в регистре OPTION

- в регистре INTCON

- (Правильный ответ) в энергонезависимой памяти данных

Какие команды микроконтроллеров подгруппы PIC16F8Х используются для организации условных переходов в программе?

- команды RETFIE и RETLW k

- команды CALL k и GOTO k

- (Правильный ответ) команды DECFSZ f, d, INCFSZ f, d, BTFSC f, b и BTFSS f, b

- любая команда

Какие команды микроконтроллеров подгруппы PIC16F8Х могут изменить все биты состояния?

- (Правильный ответ) команды ADDWF f, d , SUBWF f, d , ADDLW k и SUBLW k

- любая команда

- команды ANDWF f, d и IORWF f, d

- команды CALL k и SLEEP

Что такое «виртуальное» периферийное устройство МК?

- периферийный модуль, находящийся в стадии разработки

- периферийный модуль, поставляемый только на заказ

- периферийный модуль с изменяемыми режимами работы

- (Правильный ответ) периферийный модуль, реализованный программными средствами

Что такое «текстовая строка» в ассемблере MPASM?

- (Правильный ответ) последовательность любых допустимых ASCII символов, заключенная в двойные кавычки и длиной до 132 колонок

- последовательность любых допустимых ASCII символов, заключенная между точками с запятой, длиной до 132 колонок

- последовательность любых допустимых ASCII символов, заключенная между тире, длиной в пределах 80 колонок

- последовательность любых допустимых ASCII символов, заключенная в двойные кавычки, длиной в пределах 80 колонок

К какой шине персонального компьютера подключается больше всего устройств?

- (Правильный ответ) к системной шине

- к шине памяти

- к локальной шине

- к шине AGP

- к каждой шине подключается по одному устройству

Какая функция не выполняется программой из ROM BIOS?

- начальная загрузка операционной системы с диска

- (Правильный ответ) ускорение обмена с системной памятью

- самотестирование компьютера

- поддержка обмена с системными устройствами

- задание текущих базовых параметров аппаратуры компьютера

Какой сигнал используется для организации асинхронного обмена по магистрали ISA?

- I/O CS16

- SBHE

- AEN

- I/O CH CK

- (Правильный ответ) I/O CH RDY

Выберите неверное утверждение:

- (Правильный ответ) PCI — немультиплексированная шина

- количество слотов шины PCI мало

- PCI — быстродействующая шина

- на шине PCI возможен синхронный и асинхронный обмен

- на шине PCI предусмотрена автоконфигурация

Какое значение сигнала считывается при вводе данных с порта микроконтроллера?

- содержимое триггера регистра управления

- логическое «И» над содержимым триггера данных и значением сигнала на внешнем выводе МК

- (Правильный ответ) значение сигнала на внешнем выводе МК

- содержимое триггера данных

В какое состояние переходят порты ввода/вывода PIC-микроконтроллеров по умолчанию (после сброса)?

- в состояние вывода логического «0»

- в состояние вывода логической «1»

- в третье (высокоимпедансное) состояние

- (Правильный ответ) в состояние ввода

Какой режим обмена используется чаще всего?

- (Правильный ответ) программный обмен

- обмен по прямому доступу к памяти

- обмен по прерываниям

- все режимы используются одинаково часто

Какие действия выполняет команда CLRWDT системы команд микроконтроллеров подгруппы PIC16F8Х?

- сбрасывает контроллер

- сбрасывает в 0 содержимое сторожевого таймера

- (Правильный ответ) сбрасывает в 0 содержимое сторожевого таймера и пределителя (если он используется)

- сбрасывает в 0 содержимое счетчика команд

Что входит в транзакцию на шине PCI?

- одна или несколько фаз пересылки данных

- фаза адреса

- запрос и предоставление прерывания

- полный процесс автоконфигурации

- (Правильный ответ) фаза адреса и несколько фаз пересылки данных

Как компьютер узнает об отсутствии бумаги в принтере при использовании Centronics?

- (Правильный ответ) с помощью специального сигнала от принтера

- компьютер не может узнать об отсутствии бумаги

- принтер выдает особую комбинацию нескольких сигналов

- принтер долго не дает разрешения на обмен

- компьютер посылает специальный запрос о наличии бумаги

Какой тип обмена используется в системной магистрали ISA?

- асинхронный

- мультиплексированный

- синхронный

- (Правильный ответ) синхронный с возможностью асинхронного обмена

Что определяет директива EQU ассемблера MPASM?

- (Правильный ответ) ассемблерную константу

- равенство переменных

- начальный адрес программы

- метку замены текста

Что устанавливается на системной плате компьютера?

- системная память и контроллер дисплея

- слоты всех шин и внешние разъемы компьютера

- (Правильный ответ) основные узлы компьютера и слоты расширения

- процессор и некоторые контроллеры

- контроллер дисплея и контроллер локальной сети

Какой основной недостаток у памяти DRAM?

- большой ток потребления

- (Правильный ответ) невысокое быстродействие

- высокая цена

- малый объем памяти на одну микросхему

- память DRAM — наилучшая по всем параметрам

Что слабее других влияет на процесс обмена сигналами по магистрали?

- нельзя сказать однозначно

- радиальное прерывание

- прямой доступ к памяти

- (Правильный ответ) векторное прерывание

К какой группе команд относятся команды работы со стеком?

- арифметические команды

- (Правильный ответ) команды пересылки

- к отдельной группе

- команды переходов

- логические команды

АЦП какого типа чаще всего используют в составе микроконтроллера?

- (Правильный ответ) последовательного приближения

- на основе преобразователей напряжение-частота

- параллельные

- интегрирующие

46

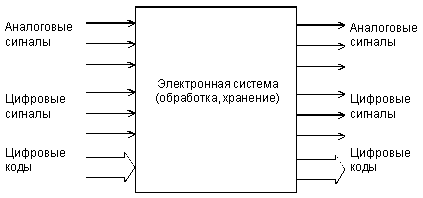

Основные определения:

Электронная

система —

в данном случае это любой электронный

узел, блок, прибор или комплекс,

производящий обработку информации.

Задача — это набор

функций, выполнение которых требуется

от электронной системы.

Быстродействие —

это показатель скорости выполнения

электронной системой ее функций.

Гибкость — это

способность системы подстраиваться

под различные задачи.

Избыточность —

это показатель степени соответствия

возможностей системы решаемой данной

системой задаче.

Интерфейс —

соглашение об обмене информацией,

правила обмена информацией, подразумевающие

электрическую, логическую и конструктивную

совместимость устройств, участвующих

в обмене. Другое название — сопряжение.

Микропроцессорная

система может рассматриваться как

частный случай электронной системы,

предназначенной для обработки входных

сигналов и выдачи выходных сигналов

(рис. 1.1). В качестве входных и выходных

сигналов при этом могут использоваться

аналоговые сигналы, одиночные цифровые

сигналы, цифровые коды, последовательности

цифровых кодов. Внутри системы может

производиться хранение, накопление

сигналов (или информации), но суть от

этого не меняется. Если система цифровая

(а микропроцессорные системы относятся

к разряду цифровых), то входные аналоговые

сигналы преобразуются в последовательности

кодов выборок с помощью АЦП, а выходные

аналоговые сигналы формируются из

последовательности кодов выборок с

помощью ЦАП. Обработка и хранение

информации производятся в цифровом

виде.

Характерная

особенность традиционной цифровой

системы состоит в том, что алгоритмы

обработки и хранения информации в ней

жестко связаны со схемотехникой системы.

То есть изменение этих алгоритмов

возможно только путем изменения структуры

системы, замены электронных узлов,

входящих в систему, и/или связей между

ними. Например, если нам нужна дополнительная

операция суммирования, то необходимо

добавить в структуру системы лишний

сумматор. Или если нужна дополнительная

функция хранения кода в течение одного

такта, то мы должны добавить в структуру

еще один регистр. Естественно, это

практически невозможно сделать в

процессе эксплуатации, обязательно

нужен новый производственный цикл

проектирования, изготовления, отладки

всей системы. Именно поэтому традиционная

цифровая система часто называется

системой на «жесткой логике».

Рис. 1.1. Электронная

система.

Любая система на

«жесткой логике» обязательно представляет

собой специализированную систему,

настроенную исключительно на одну

задачу или (реже) на несколько близких,

заранее известных задач. Это имеет свои

бесспорные преимущества.

Во-первых,

специализированная система (в отличие

от универсальной) никогда не имеет

аппаратурной избыточности, то есть

каждый ее элемент обязательно работает

в полную силу (конечно, если эта система

грамотно спроектирована).

Во-вторых, именно

специализированная система может

обеспечить максимально высокое

быстродействие, так как скорость

выполнения алгоритмов обработки

информации определяется в ней только

быстродействием отдельных логических

элементов и выбранной схемой путей

прохождения информации. А именно

логические элементы всегда обладают

максимальным на данный момент

быстродействием.

Но в то же время

большим недостатком цифровой системы

на «жесткой логике» является то, что

для каждой новой задачи ее надо

проектировать и изготавливать заново.

Это процесс длительный, дорогостоящий,

требующий высокой квалификации

исполнителей. А если решаемая задача

вдруг изменяется, то вся аппаратура

должна быть полностью заменена. В нашем

быстро меняющемся мире это довольно

расточительно.

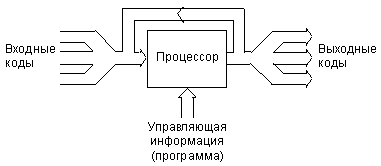

Путь преодоления

этого недостатка довольно очевиден:

надо построить такую систему, которая

могла бы легко адаптироваться под любую

задачу, перестраиваться с одного

алгоритма работы на другой без изменения

аппаратуры. И задавать тот или иной

алгоритм мы тогда могли бы путем ввода

в систему некой дополнительной управляющей

информации, программы работы системы

(рис. 1.2). Тогда система станет универсальной,

или программируемой, не жесткой, а

гибкой. Именно это и обеспечивает

микропроцессорная система.

Рис. 1.2. Программируемая

(она же универсальная) электронная

система.

Но любая

универсальность обязательно приводит

к избыточности. Ведь решение максимально

трудной задачи требует гораздо больше

средств, чем решение максимально простой

задачи. Поэтому сложность универсальной

системы должна быть такой, чтобы

обеспечивать решение самой трудной

задачи, а при решении простой задачи

система будет работать далеко не в

полную силу, будет использовать не все

свои ресурсы. И чем проще решаемая

задача, тем больше избыточность, и тем

менее оправданной становится

универсальность. Избыточность ведет к

увеличению стоимости системы, снижению

ее надежности, увеличению потребляемой

мощности и т.д.

Кроме того,

универсальность, как правило, приводит

к существенному снижению быстродействия.

Оптимизировать универсальную систему

так, чтобы каждая новая задача решалась

максимально быстро, попросту невозможно.

Общее правило таково: чем больше

универсальность, гибкость, тем меньше

быстродействие. Более того, для

универсальных систем не существует

таких задач (пусть даже и самых простых),

которые бы они решали с максимально

возможным быстродействием. За все

приходится платить.

Таким образом,

можно сделать следующий вывод. Системы

на «жесткой логике» хороши там, где

решаемая задача не меняется длительное

время, где требуется самое высокое

быстродействие, где алгоритмы обработки

информации предельно просты. А

универсальные, программируемые системы

хороши там, где часто меняются решаемые

задачи, где высокое быстродействие не

слишком важно, где алгоритмы обработки

информации сложные. То есть любая система

хороша на своем месте.

Однако за последние

десятилетия быстродействие универсальных

(микропроцессорных) систем сильно

выросло (на несколько порядков). К тому

же большой объем выпуска микросхем для

этих систем привел к резкому снижению

их стоимости. В результате область

применения систем на «жесткой логике»

резко сузилась. Более того, высокими

темпами развиваются сейчас программируемые

системы, предназначенные для решения

одной задачи или нескольких близких

задач. Они удачно совмещают в себе как

достоинства систем на «жесткой логике»,

так и программируемых систем, обеспечивая

сочетание достаточно высокого

быстродействия и необходимой гибкости.

Так что вытеснение «жесткой логики»

продолжается.

1.1. Что такое

микропроцессор?

Ядром любой

микропроцессорной системы является

микропроцессор или просто процессор

(от английского processor). Перевести на

русский язык это слово правильнее всего

как «обработчик», так как именно

микропроцессор — это тот узел, блок,

который производит всю обработку

информации внутри микропроцессорной

системы. Остальные узлы выполняют всего

лишь вспомогательные функции: хранение

информации (в том числе и управляющей

информации, то есть программы), связи с

внешними устройствами, связи с

пользователем и т.д. Процессор заменяет

практически всю «жесткую логику»,

которая понадобилась бы в случае

традиционной цифровой системы. Он

выполняет арифметические функции

(сложение, умножение и т.д.), логические

функции (сдвиг, сравнение, маскирование

кодов и т.д.), временное хранение кодов

(во внутренних регистрах), пересылку

кодов между узлами микропроцессорной

системы и многое другое. Количество

таких элементарных операций, выполняемых

процессором, может достигать нескольких

сотен. Процессор можно сравнить с мозгом

системы.

Но при этом надо

учитывать, что все свои операции процессор

выполняет последовательно, то есть одну

за другой, по очереди. Конечно, существуют

процессоры с параллельным выполнением

некоторых операций, встречаются также

микропроцессорные системы, в которых

несколько процессоров работают над

одной задачей параллельно, но это редкие

исключения. С одной стороны, последовательное

выполнение операций — несомненное

достоинство, так как позволяет с помощью

всего одного процессора выполнять

любые, самые сложные алгоритмы обработки

информации. Но, с другой стороны,

последовательное выполнение операций

приводит к тому, что время выполнения

алгоритма зависит от его сложности.

Простые алгоритмы выполняются быстрее

сложных. То есть микропроцессорная

система способна сделать все, но работает

она не слишком быстро, ведь все

информационные потоки приходится

пропускать через один-единственный

узел — микропроцессор (рис. 1.3). В

традиционной цифровой системе можно

легко организовать параллельную

обработку всех потоков информации,

правда, ценой усложнения схемы.

Рис. 1.3. Информационные

потоки в микропроцессорной системе.

Итак, микропроцессор

способен выполнять множество операций.

Но откуда он узнает, какую операцию ему

надо выполнять в данный момент? Именно

это определяется управляющей информацией,

программой. Программа представляет

собой набор команд (инструкций), то есть

цифровых кодов, расшифровав которые,

процессор узнает, что ему надо делать.

Программа от начала и до конца составляется

человеком, программистом, а процессор

выступает в роли послушного исполнителя

этой программы, никакой инициативы он

не проявляет (если, конечно, исправен).

Поэтому сравнение процессора с мозгом

не слишком корректно. Он всего лишь

исполнитель того алгоритма, который

заранее составил для него человек. Любое

отклонение от этого алгоритма может

быть вызвано только неисправностью

процессора или каких-нибудь других

узлов микропроцессорной системы.

Все команды,

выполняемые процессором, образуют

систему команд процессора. Структура

и объем системы команд процессора

определяют его быстродействие, гибкость,

удобство использования. Всего команд

у процессора может быть от нескольких

десятков до нескольких сотен. Система

команд может быть рассчитана на узкий

круг решаемых задач (у специализированных

процессоров) или на максимально широкий

круг задач (у универсальных процессоров).

Коды команд могут иметь различное

количество разрядов (занимать от одного

до нескольких байт). Каждая команда

имеет свое время выполнения, поэтому

время выполнения всей программы зависит

не только от количества команд в

программе, но и от того, какие именно

команды используются.

Для выполнения

команд в структуру процессора входят

внутренние регистры, арифметико-логическое

устройство (АЛУ, ALU — Arithmetic Logic Unit) ,

мультиплексоры, буферы, регистры и

другие узлы. Работа всех узлов

синхронизируется общим внешним тактовым

сигналом процессора. То есть процессор

представляет собой довольно сложное

цифровое устройство (рис. 1.4).

Рис. 1.4. Пример

структуры простейшего процессора.

Впрочем, для

разработчика микропроцессорных систем

информация о тонкостях внутренней

структуры процессора не слишком важна.

Разработчик должен рассматривать

процессор как «черный ящик», который в

ответ на входные и управляющие коды

производит ту или иную операцию и выдает

выходные сигналы. Разработчику необходимо

знать систему команд, режимы работы

процессора, а также правила взаимодействия

процессора с внешним миром или, как их

еще называют, протоколы обмена информацией.

О внутренней структуре процессора надо

знать только то, что необходимо для

выбора той или иной команды, того или

иного режима работы.

1.2. Шинная структура

связей

Для достижения

максимальной универсальности и упрощения

протоколов обмена информацией в

микропроцессорных системах применяется

так называемая шинная структура связей

между отдельными устройствами, входящими

в систему. Суть шинной структуры связей

сводится к следующему.

При классической

структуре связей (рис. 1.5) все сигналы и

коды между устройствами передаются по

отдельным линиям связи. Каждое устройство,

входящее в систему, передает свои сигналы

и коды независимо от других устройств.

При этом в системе получается очень

много линий связи и разных протоколов

обмена информацией.

При шинной структуре

связей (рис. 1.6) все сигналы между

устройствами передаются по одним и тем

же линиям связи, но в разное время (это

называется мультиплексированной

передачей). Причем передача по всем

линиям связи может осуществляться в

обоих направлениях (так называемая

двунаправленная передача). В результате

количество линий связи существенно

сокращается, а правила обмена (протоколы)

упрощаются. Группа линий связи, по

которым передаются сигналы или коды

как раз и называется шиной (англ. bus).

Понятно, что при

шинной структуре связей легко

осуществляется пересылка всех

информационных потоков в нужном

направлении, например, их можно пропустить

через один процессор, что очень важно

для микропроцессорной системы. Однако

при шинной структуре связей вся информация

передается по линиям связи последовательно

во времени, по очереди, что снижает

быстродействие системы по сравнению с

классической структурой связей.

Рис. 1.6. Шинная

структура связей.

Большое достоинство

шинной структуры связей состоит в том,

что все устройства, подключенные к шине,

должны принимать и передавать информацию

по одним и тем же правилам (протоколам

обмена информацией по шине). Соответственно,

все узлы, отвечающие за обмен с шиной в

этих устройствах, должны быть единообразны,

унифицированы.

Существенный

недостаток шинной структуры связан с

тем, что все устройства подключаются к

каждой линии связи параллельно. Поэтому

любая неисправность любого устройства

может вывести из строя всю систему, если

она портит линию связи. По этой же причине

отладка системы с шинной структурой

связей довольно сложна и обычно требует

специального оборудования.

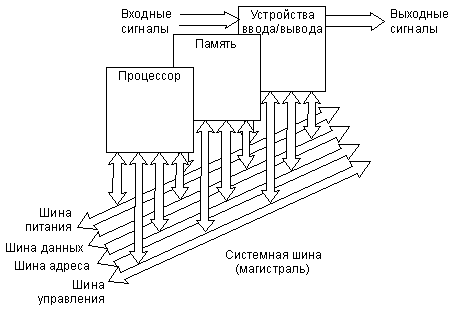

Типичная структура

микропроцессорной системы приведена

на рис. 1.10. Она включает в себя три

основных типа устройств:

процессор;

память, включающую

оперативную память (ОЗУ, RAM — Random Access

Memory) и постоянную память (ПЗУ, ROM —Read

Only Memory), которая служит для хранения

данных и программ;

устройства

ввода/вывода (УВВ, I/O — Input/Output Devices),

служащие для связи микропроцессорной

системы с внешними устройствами, для

приема (ввода, чтения, Read) входных сигналов

и выдачи (вывода, записи, Write) выходных

сигналов.

Рис. 1.10. Структура

микропроцессорной системы.

Все устройства

микропроцессорной системы объединяются

общей системной шиной (она же называется

еще системной магистралью или каналом).

Системная магистраль включает в себя

четыре основные шины нижнего уровня:

шина адреса (Address

Bus);

шина данных (Data

Bus);

шина управления

(Control Bus);

шина питания (Power

Bus).

Шина адреса служит

для определения адреса (номера) устройства,

с которым процессор обменивается

информацией в данный момент. Каждому

устройству (кроме процессора), каждой

ячейке памяти в микропроцессорной

системе присваивается собственный

адрес. Когда код какого-то адреса

выставляется процессором на шине адреса,

устройство, которому этот адрес приписан,

понимает, что ему предстоит обмен

информацией. Шина адреса может быть

однонаправленной или двунаправленной.

Шина данных — это

основная шина, которая используется

для передачи информационных кодов между

всеми устройствами микропроцессорной

системы. Обычно в пересылке информации

участвует процессор, который передает

код данных в какое-то устройство или в

ячейку памяти или же принимает код

данных из какого-то устройства или из

ячейки памяти. Но возможна также и

передача информации между устройствами

без участия процессора. Шина данных

всегда двунаправленная.

Шина управления

в отличие от шины адреса и шины данных

состоит из отдельных управляющих

сигналов. Каждый из этих сигналов во

время обмена информацией имеет свою

функцию. Некоторые сигналы служат для

стробирования передаваемых или

принимаемых данных (то есть определяют

моменты времени, когда информационный

код выставлен на шину данных). Другие

управляющие сигналы могут использоваться

для подтверждения приема данных, для

сброса всех устройств в исходное

состояние, для тактирования всех

устройств и т.д. Линии шины управления

могут быть однонаправленными или

двунаправленными.

Наконец, шина

питания предназначена не для пересылки

информационных сигналов, а для питания

системы. Она состоит из линий питания

и общего провода. В микропроцессорной

системе может быть один источник питания

(чаще +5 В) или несколько источников

питания (обычно еще –5 В, +12 В и –12 В).

Каждому напряжению питания соответствует

своя линия связи. Все устройства

подключены к этим линиям параллельно.

Если в микропроцессорную

систему надо ввести входной код (или

входной сигнал), то процессор по шине

адреса обращается к нужному устройству

ввода/вывода и принимает по шине данных

входную информацию. Если из микропроцессорной

системы надо вывести выходной код (или

выходной сигнал), то процессор обращается

по шине адреса к нужному устройству

ввода/вывода и передает ему по шине

данных выходную информацию.

Если информация

должна пройти сложную многоступенчатую

обработку, то процессор может хранить

промежуточные результаты в системной

оперативной памяти. Для обращения к

любой ячейке памяти процессор выставляет

ее адрес на шину адреса и передает в нее

информационный код по шине данных или

же принимает из нее информационный код

по шине данных. В памяти (оперативной и

постоянной) находятся также и управляющие

коды (команды выполняемой процессором

программы), которые процессор также

читает по шине данных с адресацией по

шине адреса. Постоянная память используется

в основном для хранения программы

начального пуска микропроцессорной

системы, которая выполняется каждый

раз после включения питания. Информация

в нее заносится изготовителем раз и

навсегда.

Таким образом, в

микропроцессорной системе все

информационные коды и коды команд

передаются по шинам последовательно,

по очереди. Это определяет сравнительно

невысокое быстродействие микропроцессорной

системы. Оно ограничено обычно даже не

быстродействием процессора (которое

тоже очень важно) и не скоростью обмена

по системной шине (магистрали), а именно

последовательным характером передачи

информации по системной шине (магистрали).

Важно учитывать,

что устройства ввода/вывода чаще всего

представляют собой устройства на

«жесткой логике». На них может быть

возложена часть функций, выполняемых

микропроцессорной системой. Поэтому у

разработчика всегда имеется возможность

перераспределять функции системы между

аппаратной и программной реализациями

оптимальным образом. Аппаратная

реализация ускоряет выполнение функции,

но имеет недостаточную гибкость.

Программная реализация значительно

медленнее, но обеспечивает высокую

гибкость. Аппаратная реализация функций

увеличивает стоимость системы и ее

энергопотребление, программная — не

увеличивает. Чаще всего применяется

комбинирование аппаратных и программных

функций.

Иногда устройства

ввода/вывода имеют в своем составе

процессор, то есть представляют собой

небольшую специализированную

микропроцессорную систему. Это позволяет

переложить часть программных функций

на устройства ввода/вывода, разгрузив

центральный процессор системы.

1.3. Режимы работы

микропроцессорной системы

Как уже отмечалось,

микропроцессорная система обеспечивает

большую гибкость работы, она способна

настраиваться на любую задачу. Гибкость

эта обусловлена прежде всего тем, что

функции, выполняемые системой, определяются

программой (программным обеспечением,

software), которую выполняет процессор.

Аппаратура (аппаратное обеспечение,

hardware) остается неизменной при любой

задаче. Записывая в память системы

программу, можно заставить микропроцессорную

систему выполнять любую задачу,

поддерживаемую данной аппаратурой. К

тому же шинная организация связей

микропроцессорной системы позволяет

довольно легко заменять аппаратные

модули, например, заменять память на

новую большего объема или более высокого

быстродействия, добавлять или

модернизировать устройства ввода/вывода,

наконец, заменять процессор на более

мощный. Это также позволяет увеличить

гибкость системы, продлить ее жизнь при

любом изменении требований к ней.

Но гибкость

микропроцессорной системы определяется

не только этим. Настраиваться на задачу

помогает еще и выбор режима работы

системы, то есть режима обмена информацией

по системной магистрали (шине).

Практически любая

развитая микропроцессорная система (в

том числе и компьютер) поддерживает три

основных режима обмена по магистрали:

программный обмен

информацией;

обмен с использованием

прерываний (Interrupts);

обмен с использованием

прямого доступа к памяти (ПДП, DMA — Direct

Memory Access).

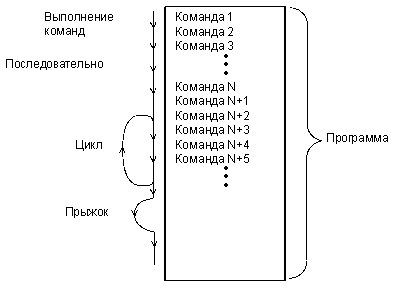

Программный обмен

информацией является основным в любой

микропроцессорной системе. Он предусмотрен

всегда, без него невозможны другие

режимы обмена. В этом режиме процессор

является единоличным хозяином (или

задатчиком, Master) системной магистрали.

Все операции (циклы) обмена информацией

в данном случае инициируются только

процессором, все они выполняются строго

в порядке, предписанном исполняемой

программой.

Процессор читает

(выбирает) из памяти коды команд и

исполняет их, читая данные из памяти

или из устройства ввода/вывода, обрабатывая

их, записывая данные в память или

передавая их в устройство ввода/вывода.

Путь процессора по программе может быть

линейным, циклическим, может содержать

переходы (прыжки), но он всегда непрерывен

и полностью находится под контролем

процессора. Ни на какие внешние события,

не связанные с программой, процессор

не реагирует (рис. 1.11). Все сигналы на

магистрали в данном случае контролируются

процессором.

Рис. 1.11. Программный

обмен информацией.

Обмен по прерываниям

используется тогда, когда необходима

реакция микропроцессорной системы на

какое-то внешнее событие, на приход

внешнего сигнала. В случае компьютера

внешним событием может быть, например,

нажатие на клавишу клавиатуры или приход

по локальной сети пакета данных. Компьютер

должен реагировать на это, соответственно,

выводом символа на экран или же чтением

и обработкой принятого по сети пакета.

В общем случае

организовать реакцию на внешнее событие

можно тремя различными путями:

с помощью постоянного

программного контроля факта наступления

события (так называемый метод опроса

флага или polling);

с помощью прерывания,

то есть насильственного перевода

процессора с выполнения текущей программы

на выполнение экстренно необходимой

программы;

с помощью прямого

доступа к памяти, то есть без участия

процессора при его отключении от

системной магистрали.

Проиллюстрировать

эти три способа можно следующим простым

примером. Допустим, вы готовите себе

завтрак, поставив на плиту кипятиться

молоко. Естественно, на закипание молока

надо реагировать, причем срочно. Как

это организовать? Первый путь — постоянно

следить за молоком, но тогда вы ничего

другого не сможете делать. Правильнее

будет регулярно поглядывать на молоко,

делая одновременно что-то другое. Это

программный режим с опросом флага.

Второй путь — установить на кастрюлю

с молоком датчик, который подаст звуковой

сигнал при закипании молока, и спокойно

заниматься другими делами. Услышав

сигнал, вы выключите молоко. Правда,

возможно, вам придется сначала закончить

то, что вы начали делать, так что ваша

реакция будет медленнее, чем в первом

случае. Наконец, третий путь состоит в

том, чтобы соединить датчик на кастрюле

с управлением плитой так, чтобы при

закипании молока горелка была выключена

без вашего участия (правда, аналогия с

ПДП здесь не очень точная, так как в

данном случае на момент выполнения

действия вас не отвлекают от работы).

Первый случай с

опросом флага реализуется в микропроцессорной

системе постоянным чтением информации

процессором из устройства ввода/вывода,

связанного с тем внешним устройством,

на поведение которого необходимо срочно

реагировать.

Во втором случае

в режиме прерывания процессор, получив

запрос прерывания от внешнего устройства

(часто называемый IRQ — Interrupt ReQuest),

заканчивает выполнение текущей команды

и переходит к программе обработки

прерывания. Закончив выполнение программы

обработки прерывания, он возвращается

к прерванной программе с той точки, где

его прервали (рис. 1.12).

Здесь важно то,

что вся работа, как и в случае программного

режима, осуществляется самим процессором,

внешнее событие просто временно отвлекает

его. Реакция на внешнее событие по

прерыванию в общем случае медленнее,

чем при программном режиме. Как и в

случае программного обмена, здесь все

сигналы на магистрали выставляются

процессором, то есть он полностью

контролирует магистраль. Для обслуживания

прерываний в систему иногда вводится

специальный модуль контроллера

прерываний, но он в обмене информацией

не участвует. Его задача состоит в том,

чтобы упростить работу процессора с

внешними запросами прерываний. Этот

контроллер обычно программно управляется

процессором по системной магистрали.

Рис. 1.12. Обслуживание

прерывания.

Естественно,

никакого ускорения работы системы

прерывание не дает. Его применение

позволяет только отказаться от постоянного

опроса флага внешнего события и временно,

до наступления внешнего события, занять

процессор выполнением каких-то других

задач.

Прямой доступ к

памяти (ПДП, DMA) — это режим, принципиально

отличающийся от двух ранее рассмотренных

режимов тем, что обмен по системной шине

идет без участия процессора. Внешнее

устройство, требующее обслуживания,

сигнализирует процессору, что режим

ПДП необходим, в ответ на это процессор

заканчивает выполнение текущей команды

и отключается от всех шин, сигнализируя

запросившему устройству, что обмен в

режиме ПДП можно начинать.

Операция ПДП

сводится к пересылке информации из

устройства ввода/вывода в память или

же из памяти в устройство ввода/вывода.

Когда пересылка информации будет

закончена, процессор вновь возвращается

к прерванной программе, продолжая ее с

той точки, где его прервали (рис. 1.13). Это

похоже на режим обслуживания прерываний,

но в данном случае процессор не участвует

в обмене. Как и в случае прерываний,

реакция на внешнее событие при ПДП

существенно медленнее, чем при программном

режиме.

Понятно, что в этом

случае требуется введение в систему

дополнительного устройства (контроллера

ПДП), которое будет осуществлять

полноценный обмен по системной магистрали

без всякого участия процессора. Причем

процессор предварительно должен сообщить

этому контроллеру ПДП, откуда ему следует

брать информацию и/или куда ее следует

помещать. Контроллер ПДП может считаться

специализированным процессором, который

отличается тем, что сам не участвует в

обмене, не принимает в себя информацию

и не выдает ее (рис. 1.14).

Рис. 1.13. Обслуживание

ПДП.

Рис. 1.14. Информационные

потоки в режиме ПДП.

В принципе контроллер

ПДП может входить в состав устройства

ввода/вывода, которому необходим режим

ПДП или даже в состав нескольких устройств

ввода/вывода. Теоретически обмен с

помощью прямого доступа к памяти может

обеспечить более высокую скорость

передачи информации, чем программный

обмен, так как процессор передает данные

медленнее, чем специализированный

контроллер ПДП. Однако на практике это

преимущество реализуется далеко не

всегда. Скорость обмена в режиме ПДП

обычно ограничена возможностями

магистрали. К тому же необходимость

программного задания режимов контроллера

ПДП может свести на нет выигрыш от более

высокой скорости пересылки данных в

режиме ПДП. Поэтому режим ПДП применяется

редко.

Если в системе уже

имеется самостоятельный контроллер

ПДП, то это может в ряде случаев существенно

упростить аппаратуру устройств

ввода/вывода, работающих в режиме ПДП.

В этом, пожалуй, состоит единственное

бесспорное преимущество режима ПДП.

1.4. Архитектура

микропроцессорных систем

До сих пор мы

рассматривали только один тип архитектуры

микропроцессорных систем — архитектуру

с общей, единой шиной для данных и команд

(одношинную, или принстонскую,

фон-неймановскую архитектуру).

Соответственно, в составе системы в

этом случае присутствует одна общая

память, как для данных, так и для команд

(рис. 1.15).

Рис. 1.15. Архитектура

с общей шиной данных и команд.

Но существует

также и альтернативный тип архитектуры

микропроцессорной системы — это

архитектура с раздельными шинами данных

и команд (двухшинная, или гарвардская,

архитектура). Эта архитектура предполагает

наличие в системе отдельной памяти для

данных и отдельной памяти для команд

(рис. 1.16). Обмен процессора с каждым из

двух типов памяти происходит по своей

шине.

Архитектура с

общей шиной распространена гораздо

больше, она применяется, например, в

персональных компьютерах и в сложных

микрокомпьютерах. Архитектура с

раздельными шинами применяется в

основном в однокристальных микроконтроллерах.

Рассмотрим некоторые

достоинства и недостатки обоих

архитектурных решений.

Архитектура с

общей шиной (принстонская, фон-неймановская)

проще, она не требует от процессора

одновременного обслуживания двух шин,

контроля обмена по двум шинам сразу.

Наличие единой памяти данных и команд

позволяет гибко распределять ее объем

между кодами данных и команд. Например,

в некоторых случаях нужна большая и

сложная программа, а данных в памяти

надо хранить не слишком много. В других

случаях, наоборот, программа требуется

простая, но необходимы большие объемы

хранимых данных. Перераспределение

памяти не вызывает никаких проблем,

главное — чтобы программа и данные

вместе помещались в памяти системы. Как

правило, в системах с такой архитектурой

память бывает довольно большого объема

(до десятков и сотен мегабайт). Это

позволяет решать самые сложные задачи.

Рис. 1.16. Архитектура

с раздельными шинами данных и команд.

Архитектура с

раздельными шинами данных и команд

сложнее, она заставляет процессор

работать одновременно с двумя потоками

кодов, обслуживать обмен по двум шинам

одновременно. Программа может размещаться

только в памяти команд, данные — только

в памяти данных. Такая узкая специализация

ограничивает круг задач, решаемых

системой, так как не дает возможности

гибкого перераспределения памяти.

Память данных и память команд в этом

случае имеют не слишком большой объем,

поэтому применение систем с данной

архитектурой ограничивается обычно не

слишком сложными задачами.

В чем же преимущество

архитектуры с двумя шинами (гарвардской)?

В первую очередь, в быстродействии.

Дело в том, что при

единственной шине команд и данных

процессор вынужден по одной этой шине

принимать данные (из памяти или устройства

ввода/вывода) и передавать данные (в

память или в устройство ввода/вывода),

а также читать команды из памяти.

Естественно, одновременно эти пересылки

кодов по магистрали происходить не

могут, они должны производиться по

очереди. Современные процессоры способны

совместить во времени выполнение команд

и проведение циклов обмена по системной

шине. Использование конвейерных

технологий и быстрой кэш-памяти позволяет

им ускорить процесс взаимодействия со

сравнительно медленной системной

памятью. Повышение тактовой частоты и

совершенствование структуры процессоров

дают возможность сократить время

выполнения команд. Но дальнейшее

увеличение быстродействия системы

возможно только при совмещении пересылки

данных и чтения команд, то есть при

переходе к архитектуре с двумя шинами.

В случае двухшинной

архитектуры обмен по обеим шинам может

быть независимым, параллельным во

времени. Соответственно, структуры шин

(количество разрядов кода адреса и кода

данных, порядок и скорость обмена

информацией и т.д.) могут быть выбраны

оптимально для той задачи, которая

решается каждой шиной. Поэтому при

прочих равных условиях переход на

двухшинную архитектуру ускоряет работу

микропроцессорной системы, хотя и

требует дополнительных затрат на

аппаратуру, усложнения структуры

процессора. Память данных в этом случае

имеет свое распределение адресов, а

память команд — свое.

Проще всего

преимущества двухшинной архитектуры

реализуются внутри одной микросхемы.

В этом случае можно также существенно

уменьшить влияние недостатков этой

архитектуры. Поэтому основное ее

применение — в микроконтроллерах, от

которых не требуется решения слишком

сложных задач, но зато необходимо

максимальное быстродействие при заданной

тактовой частоте.

1.5. Типы

микропроцессорных систем

Диапазон применения

микропроцессорной техники сейчас очень

широк, требования к микропроцессорным

системам предъявляются самые разные.

Поэтому сформировалось несколько типов

микропроцессорных систем, различающихся

мощностью, универсальностью, быстродействием

и структурными отличиями. Основные типы

следующие:

микроконтроллеры

— наиболее простой тип микропроцессорных

систем, в которых все или большинство

узлов системы выполнены в виде одной

микросхемы;

контроллеры —

управляющие микропроцессорные системы,

выполненные в виде отдельных модулей;

микрокомпьютеры

— более мощные микропроцессорные

системы с развитыми средствами сопряжения

с внешними устройствами.

компьютеры (в том

числе персональные) — самые мощные и

наиболее универсальные микропроцессорные

системы.

Четкую границу

между этими типами иногда провести

довольно сложно. Быстродействие всех

типов микропроцессоров постоянно

растет, и нередки ситуации, когда новый

микроконтроллер оказывается быстрее,

например, устаревшего персонального

компьютера. Но кое-какие принципиальные

отличия все-таки имеются.

Микроконтроллеры

представляют собой универсальные

устройства, которые практически всегда

используются не сами по себе, а в составе

более сложных устройств, в том числе и

контроллеров. Системная шина

микроконтроллера скрыта от пользователя

внутри микросхемы. Возможности подключения

внешних устройств к микроконтроллеру

ограничены. Устройства на микроконтроллерах

обычно предназначены для решения одной

задачи.

Контроллеры, как

правило, создаются для решения какой-то

отдельной задачи или группы близких

задач. Они обычно не имеют возможностей

подключения дополнительных узлов и

устройств, например, большой памяти,

средств ввода/вывода. Их системная шина

чаще всего недоступна пользователю.

Структура контроллера проста и

оптимизирована под максимальное

быстродействие. В большинстве случаев

выполняемые программы хранятся в

постоянной памяти и не меняются.

Конструктивно контроллеры выпускаются

в одноплатном варианте.

Микрокомпьютеры

отличаются от контроллеров более

открытой структурой, они допускают

подключение к системной шине нескольких

дополнительных устройств. Производятся

микрокомпьютеры в каркасе, корпусе с

разъемами системной магистрали,

доступными пользователю. Микрокомпьютеры

могут иметь средства хранения информации

на магнитных носителях (например,

магнитные диски) и довольно развитые

средства связи с пользователем

(видеомонитор, клавиатура). Микрокомпьютеры

рассчитаны на широкий круг задач, но в

отличие от контроллеров, к каждой новой

задаче его надо приспосабливать заново.

Выполняемые микрокомпьютером программы

можно легко менять.

Наконец, компьютеры

и самые распространенные из них —

персональные компьютеры — это самые

универсальные из микропроцессорных

систем. Они обязательно предусматривают

возможность модернизации, а также

широкие возможности подключения новых

устройств. Их системная шина, конечно,

доступна пользователю. Кроме того,

внешние устройства могут подключаться

к компьютеру через несколько встроенных

портов связи (количество портов доходит

иногда до 10). Компьютер всегда имеет

сильно развитые средства связи с

пользователем, средства длительного

хранения информации большого объема,

средства связи с другими компьютерами

по информационным сетям. Области

применения компьютеров могут быть

самыми разными: математические расчеты,

обслуживание доступа к базам данных,

управление работой сложных электронных

систем, компьютерные игры, подготовка

документов и т.д.

Любую задачу в

принципе можно выполнить с помощью

каждого из перечисленных типов

микропроцессорных систем. Но при выборе

типа надо по возможности избегать

избыточности и предусматривать

необходимую для данной задачи гибкость

системы.

В настоящее время

при разработке новых микропроцессорных

систем чаще всего выбирают путь

использования микроконтроллеров

(примерно в 80% случаев). При этом

микроконтроллеры применяются или

самостоятельно, с минимальной

дополнительной аппаратурой, или в

составе более сложных контроллеров с

развитыми средствами ввода/вывода.

Классические

микропроцессорные системы на базе

микросхем процессоров и микропроцессорных

комплектов выпускаются сейчас довольно

редко, в первую очередь, из-за сложности

процесса разработки и отладки этих

систем. Данный тип микропроцессорных

систем выбирают в основном тогда, когда

микроконтроллеры не могут обеспечить

требуемых характеристик.

Наконец, заметное

место занимают сейчас микропроцессорные

системы на основе персонального

компьютера. Разработчику в этом случае

нужно только оснастить персональный

компьютер дополнительными устройствами

сопряжения, а ядро микропроцессорной

системы уже готово. Персональный

компьютер имеет развитые средства

программирования, что существенно

упрощает задачу разработчика. К тому

же он может обеспечить самые сложные

алгоритмы обработки информации. Основные

недостатки персонального компьютера

— большие размеры корпуса и аппаратурная

избыточность для простых задач.

Недостатком является и неприспособленность

большинства персональных компьютеров

к работе в сложных условиях (запыленность,

высокая влажность, вибрации, высокие

температуры и т.д.). Однако выпускаются

и специальные персональные компьютеры,

приспособленные к различным условиям

эксплуатации.

Правильные ответы выделены зелёным цветом.

Все ответы: Разъясняются основные понятия микропроцессорной техники, рассматриваются принципы функционирования микропроцессорных систем, предлагаются методы проектирования микропроцессорных систем на основе микроконтроллеров.

В чем главное преимущество микропроцессорной системы?

(1) высокое быстродействие

(2) малое энергопотребление

(3) низкая стоимость

(4) высокая гибкость

Сколько видов сброса реализовано в микроконтроллерах подгруппы PIC16F8Х?

Какая сфера применения является наиболее типичной для цифровых устройств на микроконтроллерах?

(1) обработка данных эксперимента

(2) решение задач математического моделирования

(3) задачи управления объектами

(4) распознавание образов

В каком порядке следуют типы информации в ассемблерной строке?

(1) мнемоника, метки, операнды, комментарий

(2) метки, мнемоника, операнды, комментарий

(3) операнды, метки, мнемоника, комментарий

(4) метки, операнды, мнемоника, комментарий

Какая шина персонального компьютера наиболее быстрая?

(1) все шины одинаково быстрые

(2) шина памяти

(3) локальная шина

(4) все зависит от конкретной ситуации

(5) системная шина

Какой основной недостаток у памяти DRAM?

(1) невысокое быстродействие

(2) высокая цена

(3) малый объем памяти на одну микросхему

(4) большой ток потребления

(5) память DRAM — наилучшая по всем параметрам

В чем основное преимущество шины ISA перед другими шинами компьютера?

(1) большее число разрядов данных

(2) более высокое быстродействие

(3) больший выбор напряжений питания

(4) большее число слотов расширения

(5) большее число разрядов адреса

Когда компьютер начинает цикл обмена по интерфейсу Centronics?

(1) при наличии кода, требующего передачи

(2) при готовности принтера

(3) сразу после окончания предыдущего цикла обмена

(4) при поступлении запроса от принтера

Какая из приведенных операций не требует проведения цикла обмена информацией?

(1) чтение данных из памяти

(2) все операции требуют проведения цикла обмена

(3) запись данных в память

(4) чтение записи из устройства ввода-вывода

(5) чтение команды из памяти

Для чего предназначены регистры процессора?

(1) для буферизации внешних шин

(2) для выполнения арифметических операций

(3) для временного хранения информации

(4) для ускорения выборки команд из памяти

(5) для управления прерываниями

Что такое операнд?

(1) код команды

(2) адрес команды

(3) код данных

(4) адрес адреса данных

(5) адрес данных

К какой группе команд относятся команды работы со стеком?

(1) арифметические команды

(2) логические команды

(3) команды пересылки

(4) команды переходов

(5) к отдельной группе

Какие преимущества дает модульная организация микроконтроллера?

(1) повышение быстродействия

(2) снижение потребляемой мощности

(3) создание разнообразных по структуре МК в пределах одного семейства

(4) повышение надежности работы

(5) увеличение числа обслуживаемых прерываний

Какое значение сигнала считывается при вводе данных с порта микроконтроллера?

(1) содержимое триггера данных

(2) содержимое триггера регистра управления

(3) логическое «И» над содержимым триггера данных и значением сигнала на внешнем выводе МК

(4) значение сигнала на внешнем выводе МК

Какой модуль микроконтроллера прекращает работу в режиме ожидания?

(1) центральный процессор

(2) тактовый генератор

(3) таймер

(4) блок прерываний

Какой формат команд используется в семействе микроконтроллеров среднего уровня PIC16CXXX?

(1) 12 бит

(2) 14 бит

(3) 16 бит

(4) 32 бита

Какой режим обмена предполагает отключение процессора?

(1) процессор никогда не отключается

(2) программный обмен

(3) обмен по прямому доступу к памяти

(4) обмен по прерываниям

Можно ли стереть бит защиты программного кода в микроконтроллерах подгруппы PIC16F8Х?

(1) нельзя

(2) можно, только если знать идентификационный код МК

(3) только вместе с содержимым памяти программ и данных МК

(4) можно, через последовательный доступ

Что такое «программный симулятор»?

(1) программа, заменяющая МК в составе устройства

(2) средство для исполнения разработанной программы на программно-логической модели МК

(3) программа для оптимизации размещения данных в памяти МК

(4) программа, подменяющая внутреннее ЗУ программ МК

Какая система счисления принимается по умолчанию в ассемблере MPASM?

(1) двоичная

(2) восьмеричная

(3) десятичная

(4) шестнадцатеричная

Какой процессор ПК был первым полностью 32-разрядным?

(1) 8088

(2) 80286

(3) 80386

(4) 486

(5) Pentium

Какая из тактовых частот ПК обычно наименьшая?

(1) Host Bus Clock

(2) CPU Clock

(3) ISA Bus Clock

(4) PCI Bus Clock

(5) все частоты одинаковые

Какая операция на магистрали ISA не требует обмена сигналами?

(1) чтение данных из памяти

(2) запрос ПДП

(3) чтение данных из устройства ввода-вывода

(4) пересылка данных в режиме ПДП

(5) запрос прерывания

Как приемник сигнала RS-232C принимает биты данных?

(1) по фронту специального стробирующего сигнала

(2) по уровню специального стробирующего сигнала

(3) в момент поступления стартового бита

(4) с временной привязкой к стоповому биту

(5) через равные промежутки времени, начиная от стартового бита

Какой тип обмена обеспечивает гарантированную передачу информации любому исполнителю?

(1) синхронный

(2) асинхронный

(3) синхронный и асинхронный

(4) ни синхронный, ни асинхронный

Для чего нужен селектор адреса в составе модуля памяти?

(1) для выделения адресов зоны стека системы

(2) для выделения адресов памяти начальной загрузки

(3) для выделения адресов устройств ввода-вывода

(4) для выделения адресов этого модуля в адресном пространстве системы

(5) для выделения адресов кэш-памяти системы

Какой метод адресации предполагает размещение операнда внутри выполняемой программы?

(1) абсолютная адресация

(2) регистровая адресация

(3) косвенная адресация

(4) непосредственная адресация

(5) операнд всегда находится внутри программы

К какой группе относятся команды сдвига кодов?

(1) арифметические команды

(2) логические команды

(3) команды пересылки

(4) команды переходов

(5) команды управления процессором

Что отличает процессоры с RISC-архитектурой от процессоров с CISC–архитектурой?

(1) тактовая частота

(2) возможность параллельного исполнения нескольких команд

(3) система команд

(4) способ обращения к памяти команд

При каких условиях триггер переполнения таймера/счетчика генерирует запрос на прерывание микроконтроллера?

(1) при переполнении таймера/счетчика

(2) при сбросе таймера/счетчика

(3) при сбросе запроса на прерывания

(4) при переполнении таймера/счетчика, если прерывания от таймера разрешены

Какой способ тактирования микроконтроллера обеспечивает наивысшую стабильность частоты?

(1) с использованием RC-цепи

(2) с использованием кварцевого резонатора

(3) с использованием керамического резонатора

(4) с использованием LC-цепи

Что дает двухступенчатый конвейер исполнения команд в PIC-микроконтроллерах?

(1) возможность одновременной выборки и исполнения команд

(2) возможность удвоения тактовой частоты

(3) возможность параллельного исполнения двух команд

(4) возможность динамического предсказания переходов

Микропроцессорная система какого типа не обеспечивает управление внешними устройствами?

(1) микроконтроллер

(2) контроллер

(3) все типы обеспечивают управление внешними устройствами

(4) компьютер

Что может использоваться в качестве регистра назначения в системе команд микроконтроллеров подгруппы PIC16F8Х?

(1) рабочий регистр W или регистр, используемый в команде

(2) любой адресуемый регистр

(3) регистр INDF

(4) регистр FSR

Какую функцию выполняет «монитор» на плате развития?

(1) устройство для контроля напряжения питания МК

(2) простейшее средство отладки

(3) устройство для контроля температуры корпуса МК

(4) средство для крепления платы развития в устройстве

Что определяет директива ORG ассемблера MPASM?

(1) параметры листинга

(2) начальный адрес программы

(3) ассемблерную переменную

(4) программный заголовок

Какова основная функция кэш-памяти?

(1) она дополнительно увеличивает объем системной памяти

(2) она позволяет использовать защищенный режим

(3) она обеспечивает многозадачный режим

(4) она ускоряет обмен процессора с системной памятью

(5) она ускоряет обмен процессора с устройствами ввода-вывода

На основе чего организован внутренний календарь ПК?

(1) на основе системного таймера

(2) на основе часов реального времени

(3) на основе программного счетчика времени

(4) на основе сетевого таймера

Какие адресные разряды участвуют в цикле регенерации памяти?

(1) SA0…SA7

(2) SA0…SA9

(3) SA0…SA15

(4) SA0…SA19

(5) LA17…LA23

Выберите неверное утверждение:

(1) PCI — быстродействующая шина

(2) PCI — немультиплексированная шина

(3) на шине PCI возможен синхронный и асинхронный обмен

(4) на шине PCI предусмотрена автоконфигурация

(5) количество слотов шины PCI мало

При каком типе прерываний число различных прерываний может быть больше?

(1) при векторных прерываниях

(2) при радиальных прерываниях

(3) максимальное число прерываний постоянно при любом типе прерываний

(4) максимальное число прерываний не ограничено

Что такое порт?

(1) простейшее устройство ввода-вывода

(2) одно из самых сложных устройств ввода-вывода

(3) устройство связи магистрали с системной памятью

(4) буфер магистрали внутри процессора

(5) внешнее устройство, с которым осуществляется сопряжение

Какой регистр определяет адрес текущей выполняемой команды?

(1) это может быть любой из регистров

(2) специализированный регистр

(3) любой из адресных регистров

(4) регистр-аккумулятор

(5) регистр-указатель стека

Какие команды обычно не меняют флаги PSW?

(1) арифметические команды

(2) логические команды

(3) команды пересылки

(4) команды переходов

(5) все команды обязательно меняют флаги

Какая память не изменяет своего содержимого в ходе выполнения программы?

(1) память данных

(2) регистры МК

(3) энергонезависимая память данных

(4) память программ

Для чего в первую очередь предназначен модуль выходного сравнения микроконтроллера?

(1) для формирования временных интервалов заданной длительности

(2) для сравнения информации на двух портах МК

(3) для измерения интервалов времени между событиями на выходах МК

(4) для выдачи импульсов фиксированной частоты

Что используется в качестве простейшего устройства аналогового ввода информации в микроконтроллере?

(1) АЦП

(2) компаратор напряжения

(3) резистивный делитель

(4) емкостной делитель

Для каких целей используются регистры специальных функций PIC-микроконтроллера?

(1) для управления работой МК

(2) для реализации специальных команд МК

(3) для хранения промежуточных данных

(4) для защиты от несанкционированного доступа

Какие команды микроконтроллеров подгруппы PIC16F8Х используются для организации условных переходов в программе?

(1) команды DECFSZ f, d, INCFSZ f, d, BTFSC f, b и BTFSS f, b

(2) команды RETFIE и RETLW k

(3) команды CALL k и GOTO k

(4) любая команда

Для чего используется файл инициализации .INI при работе симулятора MPSIM?

(1) для запуска процесса симуляции МК

(2) для задания всех используемых в программе параметров

(3) для моделирования внешних воздействий

(4) для ограничения времени симуляции

Каков типичный объем памяти данных микроконтроллера?

(1) единицы бит

(2) десятки и сотни байт

(3) десятки килобайт

(4) мегабайты

Где хранится содержимое младшего байта счетчика команд микроконтроллеров подгруппы PIC16F8Х?

(1) в регистре STATUS

(2) в регистре OPTION

(3) в регистре PCLATH

(4) в регистре PCL

Какова разрядность портов ввода/вывода микроконтроллеров подгруппы PIC16F8Х?

(1) порт А – 8 разрядов и порт В – 5 разрядов

(2) порт А – 8 разрядов и порт В – 8 разрядов

(3) порт А – 5 разрядов и порт В – 8 разрядов

(4) порт А – 5 разрядов и порт В – 5 разрядов

Какова разрядность таймера/счетчика TMR0 микроконтроллеров подгруппы PIC16F8Х?

(1) 4

(2) 8

(3) 14

(4) 16

Когда происходит инкремент таймера/счетчика в режиме счетчика без пределителя в микроконтроллерах подгруппы PIC16F8Х?

(1) каждый такт

(2) каждые 8 тактов

(3) при смене сигнала на входе T0CKI

(4) каждый командный цикл

Какие регистры управляют процессом чтения и записи энергонезависимой памяти данных микроконтроллеров подгруппы PIC16F8Х?

(1) регистр EEDATA

(2) регистр EEADR

(3) регистры EECON1 и EECON2

(4) регистры INTCON и EEADR

Разрядность какой шины прямо определяет быстродействие микропроцессорной системы?

(1) шины адреса

(2) шины данных

(3) шины управления

(4) шины питания

От какого генератора работает сторожевой таймер в микроконтроллерах подгруппы PIC16F8Х?

(1) от тактового генератора МК

(2) от собственного внутреннего RC-генератора

(3) от внешнего генератора

(4) от собственного внутреннего кварцевого генератора

Что включает в себя понятие «работа в реальном времени»?

(1) максимально достижимое на данный момент быстродействие

(2) обеспечение реакции на внешние события в течение определенного интервала времени

(3) возможность выдачи сигналов строго определенной длительности

(4) включение и выключение устройства по сигналам точного времени

Какова максимальная длина ассемблерной строки ассемблера MPASM?

(1) 80

(2) 128

(3) 255

(4) 512

К какой шине персонального компьютера подключается больше всего устройств?

(1) к шине памяти

(2) к локальной шине

(3) к шине AGP

(4) к системной шине

(5) к каждой шине подключается по одному устройству

Какая функция не выполняется программой из ROM BIOS?

(1) начальная загрузка операционной системы с диска

(2) самотестирование компьютера

(3) ускорение обмена с системной памятью

(4) задание текущих базовых параметров аппаратуры компьютера

(5) поддержка обмена с системными устройствами

Какой сигнал используется для организации асинхронного обмена по магистрали ISA?

(1) I/O CH RDY

(2) I/O CS16

(3) I/O CH CK

(4) AEN

(5) SBHE

Как компьютер узнает об отсутствии бумаги в принтере при использовании Centronics?

(1) с помощью специального сигнала от принтера

(2) принтер долго не дает разрешения на обмен

(3) компьютер посылает специальный запрос о наличии бумаги

(4) компьютер не может узнать об отсутствии бумаги

(5) принтер выдает особую комбинацию нескольких сигналов

Какой тип обмена обеспечивает более высокую скорость передачи информации?

(1) синхронный

(2) асинхронный

(3) нельзя сказать однозначно

(4) синхронный обмен с возможностью асинхронного обмена

Для чего служит регистр признаков?

(1) для хранения флагов результатов выполненных операций

(2) для хранения кодов специальных команд

(3) для хранения кода адреса

(4) для определения режима работы микропроцессорной системы

(5) для обслуживания стека

Какой метод адресации наиболее удобен для последовательной обработки массивов данных?

(1) абсолютная адресация

(2) непосредственная адресация

(3) автоинкрементная адресация

(4) косвенно-регистровая адресация

(5) прямая адресация

Для чего используются команды программных прерываний?

(1) для управления устройствами ввода-вывода

(2) для обработки аварийных ситуаций

(3) для вызова подпрограмм

(4) для управления режимами работы процессора

(5) для управления режимами работы памяти

Какие возможности отсутствуют при использовании микроконтроллеров с «закрытой» архитектурой?

(1) возможность изменения тактовой частоты МК

(2) возможность подключения памяти программ и данных по параллельным магистралям

(3) возможность использования всей совокупности системы команд МК

(4) возможность подключения внешних устройств

Какой тип логической функции позволяет реализовать объединение «квазидвунаправленных» выходов микроконтроллера?

(1) сложение по модулю 2

(2) «И»

(3) «ИЛИ»

(4) константа «1»

Как зависит ток потребления микроконтроллера от напряжения питания?

(1) не зависит

(2) приблизительно линейно

(3) обратно пропорционально

(4) квадратично

Какая архитектура используется в PIC-микроконтроллерах?

(1) фон-неймановская с RISC-процессором

(2) фон-неймановская с СISC-процессором

(3) гарвардская с RISC-процессором

(4) гарвардская с CISC-процессором

Какой режим обмена обеспечивает наибольшую скорость передачи информации?

(1) обмен по прямому доступу к памяти

(2) программный обмен

(3) обмен по прерываниям

(4) все режимы одинаковы по быстродействию

Где хранятся биты конфигурации микроконтроллеров подгруппы PIC16F8Х?

(1) в энергонезависимой памяти данных

(2) в регистре OPTION

(3) в регистре EEDATA

(4) в регистре INTCON

Что такое «внутрисхемный эмулятор»?

(1) программа для контроля состояния внутренних регистров МК

(2) аппаратное устройство для реализации пошагового режима работы МК

(3) программно-аппаратное средство для замены МК в реальной схеме

(4) программа, подменяющая внутреннее ЗУ программ МК

Что определяет директива #DEFINE ассемблера MPASM?

(1) систему счисления

(2) метку замены текста

(3) тип контроллера

(4) ассемблерную константу

Какая фирма является основным поставщиком процессоров для персональных компьютеров?

(1) IBM

(2) Intel

(3) Motorola

(4) Apple

(5) Toshiba

Сколько всего прерываний может быть в ПК?

(1) 8

(2) 16

(3) 32

(4) 64

(5) 256

Что такое удлиненный цикл обмена?

(1) цикл записи данных в память

(2) цикл чтения данных из устройства ввода-вывода

(3) цикл регенерации

(4) цикл с использованием сигнала I/O CH RDY

(5) цикл с использованием сигнала I/O CS16

Что входит в транзакцию на шине PCI?

(1) фаза адреса и несколько фаз пересылки данных

(2) одна или несколько фаз пересылки данных

(3) полный процесс автоконфигурации

(4) фаза адреса

(5) запрос и предоставление прерывания

Какой тип прерываний требует более сложной аппаратуры устройства-исполнителя?

(1) векторный

(2) радиальный

(3) тактируемый

(4) сложность не зависит от типа прерывания

Каков принцип работы стековой памяти?

(1) первый записанный код читается первым

(2) первый записанный код читается последним

(3) запись и чтение могут следовать в произвольном порядке

(4) содержимое стековой памяти не меняется за время работы системы

(5) стековая память ускоряет работу памяти векторов прерываний

Каково разделение функций между внутренними регистрами процессора?

(1) назначение регистров зависит от типа процессора

(2) все регистры выполняют одни и те же функции

(3) половина регистров используется для данных, половина — для адресации

(4) каждый регистр выполняет свою функцию

(5) одни регистры специализированные, другие — универсальные

Какие команды не формируют выходной операнд?

(1) арифметические команды

(2) логические команды

(3) команды пересылки

(4) команды переходов

(5) команды сдвигов

Каково типичное соотношение между требуемыми объемами памяти программ и данных микроконтроллера?

(1) объем памяти данных больше объема памяти программ

(2) объем памяти данных меньше объема памяти программ

(3) объем памяти данных равен объему памяти программ

(4) типичное соотношение отсутствует

Для чего в первую очередь предназначен модуль входного захвата микроконтроллера?

(1) для отслеживания изменений сигнала на входе МК

(2) для подсчета количества событий на входе МК

(3) для измерения временных интервалов между событиями на входах МК

(4) для выдачи импульсов фиксированной продолжительности

Зачем нужна задержка времени при запуске тактового генератора микроконтроллера?

(1) для стабилизации частоты генератора

(2) для минимизации энергопотребления при запуске МК

(3) для перевода регистров МК в начальное состояние

(4) для исключения выдачи ложных сигналов на выходах МК

Сколько тактов занимает выполнение одного командного цикла PIC-микроконтроллером?

Какая архитектура обеспечивает более высокое быстродействие?

(1) принстонская

(2) гарвардская

(3) фон-неймановская

(4) быстродействие не зависит от архитектуры

Какие команды микроконтроллеров подгруппы PIC16F8Х могут изменить все биты состояния?

(1) команды CALL k и SLEEP

(2) команды ANDWF f, d и IORWF f, d

(3) команды ADDWF f, d , SUBWF f, d , ADDLW k и SUBLW k

(4) любая команда

Что такое «эмулятор ПЗУ»?

(1) устройство для расширения объема внешней памяти МК

(2) устройство для «вскрытия» содержимого памяти программ МК

(3) схема для сопряжения МК с внешней памятью программ

(4) программно-аппаратное средство для замещения ПЗУ

Что использует в своей работе симулятор MPSIM?

(1) файл листинга программы

(2) выходной файл ошибок

(3) выходные данные ассемблера MPASM

(4) ассемблерный файл

В каких случаях кэш-память малоэффективна?

(1) когда в исполняемой программе много переходов

(2) когда в исполняемой программе мало переходов

(3) когда объем системной памяти компьютера невелик

(4) когда системная память имеет малое быстродействие

(5) когда объем системной памяти компьютера очень большой

Какие коды и когда вырабатываются клавиатурой?

(1) при нажатии — коды символов, соответствующих клавишам

(2) при нажатии — коды номеров клавиш

(3) при нажатии и отпускании — коды символов, соответствующих клавишам

(4) при нажатии и отпускании — коды номеров клавиш

(5) при отпускании — коды символов, соответствующих клавишам

Что подразумевает технология PnP?

(1) распределение ресурсов с помощью переключателей на плате

(2) распределение ресурсов с помощью программы-драйвера платы

(3) автоматическое распределение ресурсов

(4) отсутствие распределения ресурсов

(5) распределение ресурсов изготовителем компьютера

Какое главное преимущество интерфейса USB?

(1) максимальная скорость обмена

(2) минимальное число соединительных проводов

(3) максимальная длина соединительного кабеля

(4) скоростная последовательная передача

(5) максимально простой протокол обмена

Какой параметр слабее других влияет на процесс обмена сигналами по магистрали?

(1) длина линии связи магистрали

(2) отражение сигналов от концов линий связи

(3) положительная или отрицательная логика шины данных

(4) различие длин линий связи магистрали

(5) неодновременное выставление сигналов на линиях шины

Какое устройство не относится к устройствам ввода-вывода?

(1) контроллер видеомонитора

(2) устройство сопряжения клавиатуры

(3) интерфейсная плата локальной сети

(4) адаптер дискового накопителя

(5) селектор адреса

Какой регистр процессора 8086/8088 определяет адрес ввода/вывода?

(1) АХ

(2) BX

(3) CX

(4) DX

(5) CS

К какой группе относится команда «Исключающее ИЛИ«?

(1) арифметические команды

(2) логические команды

(3) команды пересылки

(4) команды переходов

(5) команды загрузки

Сколько раз можно изменить содержимое памяти программ на основе ПЗУ масочного типа?

(1) неограниченное число раз

(2) один раз на стадии изготовления МК

(3) один раз на стадии программирования пользователем

(4) около 1000 раз